Computers and Technology, 08.12.2020 16:40 oprajapati

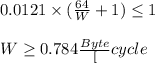

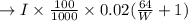

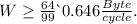

A. Suppose a CPU with a write-through, write-allocate cache achieves a CPI of 2. What are the read and write bandwidths (measured by bytes per cycle) between RAM and the cache?

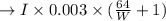

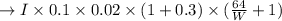

b. For a write-back, write allocate cache, assuming 30% of replaced data cache blocks are dirty, what are the read and write bandwidths needed for a CPI of 2?

Data Reads per 1000 instructions Data Writes per 1000 instructions Instruction Cahce Miss Rate Data Cache Miss Rate Block size (Bytes)

250 100 0.30% 2% 64

Answers: 2

Another question on Computers and Technology

Computers and Technology, 21.06.2019 21:30

What’s the process of observing someone actually working in a career that interests you?

Answers: 1

Computers and Technology, 23.06.2019 09:30

Write an essay on online collaboration, how to do it, the challenges, resolving the challenges, and consider whether the risks are greater than rewards. ( need )

Answers: 1

Computers and Technology, 24.06.2019 00:50

Which player type acts on other players? a. killer b. achiever c. explorer d. socializer

Answers: 1

Computers and Technology, 25.06.2019 03:30

What best describes the purpose of occupational safety and health administration

Answers: 1

You know the right answer?

A. Suppose a CPU with a write-through, write-allocate cache achieves a CPI of 2. What are the read a...

Questions

Mathematics, 02.01.2020 10:31

English, 02.01.2020 10:31

Mathematics, 02.01.2020 10:31

Mathematics, 02.01.2020 10:31

Mathematics, 02.01.2020 10:31

Mathematics, 02.01.2020 10:31

Mathematics, 02.01.2020 10:31

Social Studies, 02.01.2020 10:31

History, 02.01.2020 10:31

Mathematics, 02.01.2020 10:31

English, 02.01.2020 11:31

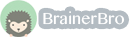

, Hit time + miss penalty Hit time:

, Hit time + miss penalty Hit time:![= I + I \times [0.25 \times 0.02 + 0.1 \times 0.02 + 0.003] \times (\frac{64}{W} + 1) \leq I \times 2.](/tpl/images/0960/7133/03573.png)

![= I + I \times [0.25 \times 0.02 \times 1.3 + 0.1 \times 0.02\times 1.3 + 0.003]\times (\frac{64}{W} + 1) \leq 2I](/tpl/images/0960/7133/32a7d.png)